是什么原因造成晶振相噪惡化?都有哪些優化策略

來源:http://www.robbia.com.cn 作者:泰河盛電子 2021年01月13

是什么原因造成晶振相噪惡化?都有哪些優化策略.

對于Oscillator產品來說,相位噪聲是一項非常重要的性能特征,它對晶振的輸出頻率穩定性影響非常大,一般情況下,相位噪聲越小,則表示晶振性能越好,輸出信號穩定性越高,所以低相噪是未來的產品發展方向;但是在優化相噪之前或者是做策略之前必須要先了解是什么原因造成了相噪的惡化,這樣才能對癥下藥.

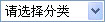

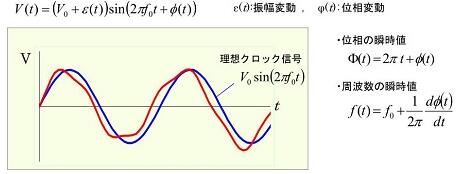

事實上,從某種意義上來看石英晶體振蕩器的相噪和抖動是一樣的,只是兩者是對同種現象的兩種不同的定量方式罷了.圖1顯示了具有理想正弦波相位項加相位變化Φ(t)形式的相位噪聲的信號波形V(t).相位噪聲和相位抖動是在頻率區域和時間區域中獲得的相位波動Φ(t). 相位噪聲以相位波動Φ(t)的頻率區域表示,并由Φ(t)的功率譜密度SΦ定義.實際上,通常使用在單邊帶中表示的SSB(單邊帶)相位噪聲L(f),載波信號與總功率的比值以dBc/Hz計算,以相對于載波頻率的偏移為水平軸.代表.

晶體振蕩器的相位噪聲在很大程度上取決于晶體振蕩器的Q值和信號電平以及振蕩電路的噪聲性能.

晶體振蕩器的相位噪聲在很大程度上取決于晶體振蕩器的Q值和信號電平以及振蕩電路的噪聲性能.

晶體振蕩器的Q值對于改善相位噪聲的載波頻率附近的相位噪聲尤其重要.無論偏移頻率如何,信號電平越高,相位噪聲電平越低.通過將信號電平設置為盡可能大的系統,可以降低相位噪聲,但是可以應用于晶體振蕩器的激勵電平存在上限.如果激勵水平過高,則可能會發生不必要的振動模式,并且振蕩狀態可能會變得異常.

泛音具有較高的Q值,并且在偏移附近很有效,但是要小心,因為在高激勵電平下工作時,石英晶振和振蕩電路的電阻損耗會變大,頻率波動會變大,并且信號純度會下降是必然的.

另外,隨著功率的增加,由于晶體換能器的非線性引起的頻率波動增加,因此在過度激勵水平下的操作也會引起相位噪聲的惡化.重要的是選擇具有優異噪聲性能的半導體器件.閃爍噪聲會影響距載波附近大約10kHz中頻附近的偏移頻率,而熱噪聲會像信號電平一樣均勻地影響整個偏移頻帶.

既然問題已經分析得差不多了,那么接下來就來看看應該怎么樣優化有源晶振的這一性能了;首先要確保石英晶振振蕩振動電路的Q值,晶體振蕩器的Q值越高,振蕩電路的電阻損耗越小,振蕩環路的Q值越高;設備降噪是必須的,選擇具有低噪聲指數NF和閃爍轉折頻率的器件,以減少半導體噪聲,例如熱噪聲,散粒噪聲和閃爍噪聲.

除此之外,PLL電路的倍頻會導致相位噪聲惡化.這點也要注意;同時還要盡可能增加振蕩電路的激勵水平.由于噪聲特性是信號電平與噪聲功率之間的相對值,所以信號電平越高,則越有利.然而,在平坦區域中使用晶體振蕩器的激發能級特性是一個條件.泛音具有較高的Q值,在偏移附近非常有用.但是,當在高激勵電平下工作時,晶體和振蕩電路的電阻損耗會增加,并且由于頻率波動,相位噪聲會惡化,因此必須小心.

最后就是適當地在距電源和GND端子最短的地方放置一個旁路電容器,以抑制電源噪聲.以上這些方法都能夠很好的優化有源晶振相噪性能,對其性能的提升大有裨益.

由此看來,要優化有源晶振系列相位噪聲,必須要注意的是晶體振蕩器振蕩電路的Q值,信號電平(也就是激勵水平,值越大對降低相噪越有益);這兩點可以說是主要決定性因素;當然,除開這兩點之外,還要注意PLL電路的倍頻;基本上能夠影響相位噪聲的就這三個方面的因素了,要優化的話也得從這三方面入手.

是什么原因造成晶振相噪惡化?都有哪些優化策略.

對于Oscillator產品來說,相位噪聲是一項非常重要的性能特征,它對晶振的輸出頻率穩定性影響非常大,一般情況下,相位噪聲越小,則表示晶振性能越好,輸出信號穩定性越高,所以低相噪是未來的產品發展方向;但是在優化相噪之前或者是做策略之前必須要先了解是什么原因造成了相噪的惡化,這樣才能對癥下藥.

事實上,從某種意義上來看石英晶體振蕩器的相噪和抖動是一樣的,只是兩者是對同種現象的兩種不同的定量方式罷了.圖1顯示了具有理想正弦波相位項加相位變化Φ(t)形式的相位噪聲的信號波形V(t).相位噪聲和相位抖動是在頻率區域和時間區域中獲得的相位波動Φ(t). 相位噪聲以相位波動Φ(t)的頻率區域表示,并由Φ(t)的功率譜密度SΦ定義.實際上,通常使用在單邊帶中表示的SSB(單邊帶)相位噪聲L(f),載波信號與總功率的比值以dBc/Hz計算,以相對于載波頻率的偏移為水平軸.代表.

晶體振蕩器的Q值對于改善相位噪聲的載波頻率附近的相位噪聲尤其重要.無論偏移頻率如何,信號電平越高,相位噪聲電平越低.通過將信號電平設置為盡可能大的系統,可以降低相位噪聲,但是可以應用于晶體振蕩器的激勵電平存在上限.如果激勵水平過高,則可能會發生不必要的振動模式,并且振蕩狀態可能會變得異常.

泛音具有較高的Q值,并且在偏移附近很有效,但是要小心,因為在高激勵電平下工作時,石英晶振和振蕩電路的電阻損耗會變大,頻率波動會變大,并且信號純度會下降是必然的.

另外,隨著功率的增加,由于晶體換能器的非線性引起的頻率波動增加,因此在過度激勵水平下的操作也會引起相位噪聲的惡化.重要的是選擇具有優異噪聲性能的半導體器件.閃爍噪聲會影響距載波附近大約10kHz中頻附近的偏移頻率,而熱噪聲會像信號電平一樣均勻地影響整個偏移頻帶.

既然問題已經分析得差不多了,那么接下來就來看看應該怎么樣優化有源晶振的這一性能了;首先要確保石英晶振振蕩振動電路的Q值,晶體振蕩器的Q值越高,振蕩電路的電阻損耗越小,振蕩環路的Q值越高;設備降噪是必須的,選擇具有低噪聲指數NF和閃爍轉折頻率的器件,以減少半導體噪聲,例如熱噪聲,散粒噪聲和閃爍噪聲.

除此之外,PLL電路的倍頻會導致相位噪聲惡化.這點也要注意;同時還要盡可能增加振蕩電路的激勵水平.由于噪聲特性是信號電平與噪聲功率之間的相對值,所以信號電平越高,則越有利.然而,在平坦區域中使用晶體振蕩器的激發能級特性是一個條件.泛音具有較高的Q值,在偏移附近非常有用.但是,當在高激勵電平下工作時,晶體和振蕩電路的電阻損耗會增加,并且由于頻率波動,相位噪聲會惡化,因此必須小心.

最后就是適當地在距電源和GND端子最短的地方放置一個旁路電容器,以抑制電源噪聲.以上這些方法都能夠很好的優化有源晶振相噪性能,對其性能的提升大有裨益.

由此看來,要優化有源晶振系列相位噪聲,必須要注意的是晶體振蕩器振蕩電路的Q值,信號電平(也就是激勵水平,值越大對降低相噪越有益);這兩點可以說是主要決定性因素;當然,除開這兩點之外,還要注意PLL電路的倍頻;基本上能夠影響相位噪聲的就這三個方面的因素了,要優化的話也得從這三方面入手.

是什么原因造成晶振相噪惡化?都有哪些優化策略.

正在載入評論數據...

相關資訊

- [2023-07-12]康納溫菲爾德推出符合Stratum3E...

- [2023-06-26]選擇石英晶體要了解的必要參數,...

- [2023-06-25]艾伯康公司發布連續電壓有源晶振...

- [2021-01-18]今日主題:什么樣性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪惡化?都...

- [2020-12-09]干貨干貨!愛普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎樣的,這...

- [2020-09-01]Oscillator的制造流程究竟是怎樣...